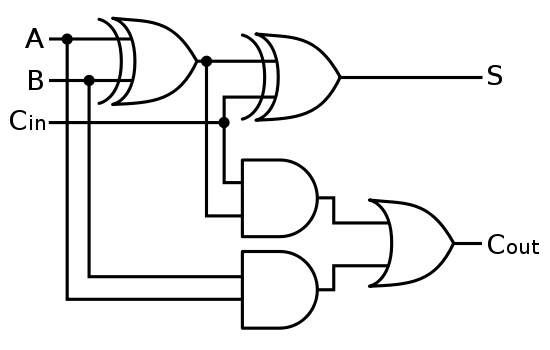

Design Full Adder Circuit

Introduction to full adder Adder vhdl circuits truth ckt Vhdl tutorial – 10: designing half and full-adder circuits

Full Adder : Circuit Diagram, Truth Table, Equations & Verilog Code

Full adder Design full adder using 3:8 decoder with active low outputs and nand gates. Digital logic design: full adder circuit

Full adder : circuit diagram, truth table, equations & verilog code

Adder cmos vlsi circuits circuit implement stackAdder logic truth gates projectiot123 half sum Decoder adder using nand gates implement circuit active low outputs logical comment add linkAdder circuit diagram basic gates using truth table.

Adder logic half implementationAdder circuit logic using digital boolean implementation function diagram implement Adder circuit logic gates construction binary circuits equations sourav guptaHalf adder and full adder circuit.

Full adder circuit: theory, truth table & construction

Adder sum simplified implementation logic combinational circuitsAdder half circuit diagram table block electronics input outputs along .

.